Materiały dydaktyczne z części wykładowej i projektowej z przedmiotu "Anteny i propagacja fal". Studia inżynierskie - semestr 3, kierunek Elektronika i Telekomunikacja

- Nauczyciel: Sławomir Jerzy Ambroziak

- Nauczyciel: SEBASTIAN Dziedziewicz

- Nauczyciel: MACIEJ Jasiński

- Nauczyciel: Rafał Lech

- start zajęć 10 listopada

- terminy zajęć 10.11, 17.11, 24.11, 1.12 --> w tych wszystkich dniach godz. 13-14 w sali EA07 i 14-15 w sali EA20

terminy zajęć 18.11, 25.11, 2.12 --> w tych wszystkich dniach godz. 13-15 w sali NE232

Kurs pomocniczy dla przedmiotu Systemy Sygnalizacji i Protokoły realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Kurs pomocniczy dla przedmiotu Projektowanie Usług Telekomunikacyjnych realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Zajęcia uzupełniające.

- Nauczyciel: Piotr Grall

Kurs przeznaczony jest dla studentów VI semestru studiów pierwszego stopnia (inżynierskich) dla przedmiotu Systemy radiokomunikacyjne - projekt.

- Nauczyciel: Andrzej Marczak

Celem przedmiotu jest wprowadzenie do projektowania systemu światłowodowego z uwzględnieniem jego najważniejszych elementów (włókno światłowodowe, nadajnik, odbiornik, sprzęgacze, wzmacniacze optyczne) oraz sposobów jego testowania.

Kurs przeznaczony jest dla studentów kierunku Elektronika i Telekomunikacja (studia I stopnia - inżynierskie, stacjonarne).

- Nauczyciel: Piotr Kowalczyk

- Nauczyciel: Łukasz Kulas

I stopień, Strumień EA, EiT, sem.5

- Nauczyciel: Agnieszka Drewniak

- Nauczyciel: Piotr Jasiński

- Nauczyciel: PAWEŁ Kalinowski

- Nauczyciel: KRYSTIAN Lankauf

- Nauczyciel: KAMIL Osiński

Materiały do wykładu i ćwiczeń z przedmiotu

- Nauczyciel: ARTUR Gańcza

- Nauczyciel: Piotr Kaczmarek

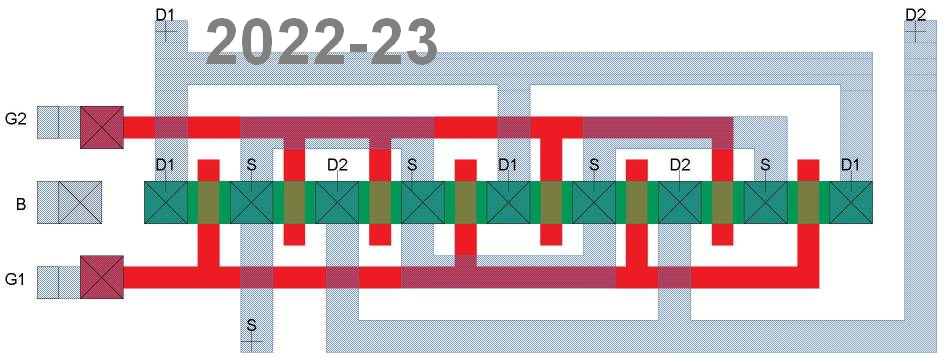

Cel przedmiotu: Zapoznanie z metodami projektowania i symulacji cyfrowych układów programowalnych i ASIC z wykorzystaniem języków opisu sprzętu.

Treści przedmiotu:

1. Wprowadzenie, znaczenie i zastosowania języków HDL. Historia powstania języka Verilog.

2. Poziomy opisu sprzętu (Verilog).

3. Metodologie projektowania. Prosty przykład.

4. Składnia języka Verilog.

5. Typy danych.

6. Zadania systemowe i dyrektywy kompilatora.

7. Moduły i porty.

8. Projektowanie na poziomie bramek logicznych.

9. Opóźnienia w bramkach.

10. Modelowanie na poziomie rejestrów.

11. Przypisanie ciągłe.

12. Wyrażenia i operatory.

13. Modelowanie na poziomie behawioralnym.

14. Funkcje i zadania.

15. Techniki modelowania.

16. Verilog 2001 zmiany w standardzie.

17. Geneza powstania języka VHDL.

18. Składnia języka i typy danych

19. Jednostki projektowe i ich architektury.

20. Osadzanie komponentów.

21. Przypisania współbieżne, zwykłe i warunkowe.

22. Opóźnienia, operacje współbieżne oraz czasowe.

23. Procesy.

24. Polecenia warunkowe i pętle.

25. Opóźnienia typu wait.

26. Funkcje i procedury.

27. Biblioteki i pakiety.

28. Biblioteka IEEE.

29. Synteza maszyn stanów.

- Nauczyciel: Marek Wójcikowski

- Nauczyciel: TOMASZ Chludziński

- Nauczyciel: Barbara Stawarz-Graczyk

- Nauczyciel: Arkadiusz Szewczyk

EiT studia I stopinia, sem. zimowy 21/22

- Nauczyciel: Natalia Kowalczyk

- Nauczyciel: Magdalena Mazur-Milecka

- Nauczyciel: Jacek Rumiński

- Nauczyciel: Jakub Gierowski

- Nauczyciel: Marcin Gnyba

- Nauczyciel: KATARZYNA Karpienko

- Nauczyciel: MONIKA Kosowska

- Nauczyciel: Paulina Listewnik

- Nauczyciel: DARIA Majchrowicz

- Nauczyciel: Adam Mazikowski

- Nauczyciel: Sandra Pawłowska

- Nauczyciel: Małgorzata Szczerska

- Nauczyciel: Małgorzata Gajewska

- Nauczyciel: Sławomir Gajewski

- Nauczyciel: Ryszard Katulski

Projekt dla studentów semestru 6 studiów 1. stopnia, kierunek: Telekomunikacja.

Studenci samodzielnie realizują zadania związane z uruchamianiem podstawowych algorytmów cyfrowego przetwarzania sygnałów na procesorze sygnałowym. Wykorzystywane są następujące algorytmy: generowanie sygnałów, filtracja FIR i IIR, analiza widmowa. W trakcie realizacji projektu studenci nabywają praktyczną wiedzę w zakresie: implementacji algorytmów przetwarzania sygnałów w postaci kodu w języku C; uruchamiania algorytmów na procesorze sygnałowym; testowania poprawności działania algorytmów, znajdowania i poprawiania błędów; interpretacji uzyskiwanych wyników.

Prowadzący: dr hab. inż. Grzegorz Szwoch, dr. inż. Piotr Odya, mgr inż. Adam Kurowski

- Nauczyciel: Piotr Odya

- Nauczyciel: Grzegorz Szwoch

Telekomunikacja, 6. semestr, studia I stopnia

- Nauczyciel: Sebastian Cygert

- Nauczyciel: Andrzej Czyżewski

- Nauczyciel: Józef Kotus

- Nauczyciel: Adam Kurowski

- Nauczyciel: Michał Lech

- Nauczyciel: Piotr Szczuko

- Nauczyciel: Szymon Zaporowski

Telekomunikacja, 5. semestr, studia I stopnia

- Nauczyciel: Sebastian Cygert

- Nauczyciel: Andrzej Czyżewski

- Nauczyciel: Arkadiusz Harasimiuk

- Nauczyciel: Bożena Kostek

- Nauczyciel: Józef Kotus

- Nauczyciel: Piotr Odya

- Nauczyciel: PIOTR Sokołowski

- Nauczyciel: Maciej Szczodrak

- Nauczyciel: Piotr Szczuko

- Nauczyciel: Grzegorz Szwoch

- Nauczyciel: Szymon Zaporowski

- Nauczyciel: Sebastian Cygert

- Nauczyciel: Andrzej Czyżewski

- Nauczyciel: Franciszek Górski

- Nauczyciel: Arkadiusz Harasimiuk

- Nauczyciel: BARTŁOMIEJ Mróz

- Nauczyciel: Piotr Odya

- Nauczyciel: PIOTR Sokołowski

- Nauczyciel: Maciej Szczodrak

- Nauczyciel: Grzegorz Szwoch

- Nauczyciel: Jacek Jakusz