Kurs pomocniczy dla przedmiotu Projektowanie Usług Telekomunikacyjnych realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Telekomunikacja, 5. semestr, studia I stopnia

- Nauczyciel: Sebastian Cygert

- Nauczyciel: Andrzej Czyżewski

- Nauczyciel: Arkadiusz Harasimiuk

- Nauczyciel: Bożena Kostek

- Nauczyciel: Józef Kotus

- Nauczyciel: Wanda Ludwikowska

- Nauczyciel: Piotr Odya

- Nauczyciel: PIOTR Sokołowski

- Nauczyciel: PIOTR SOKOŁOWSKI

- Nauczyciel: Maciej Szczodrak

- Nauczyciel: Piotr Szczuko

- Nauczyciel: Grzegorz Szwoch

- Nauczyciel: Szymon Zaporowski

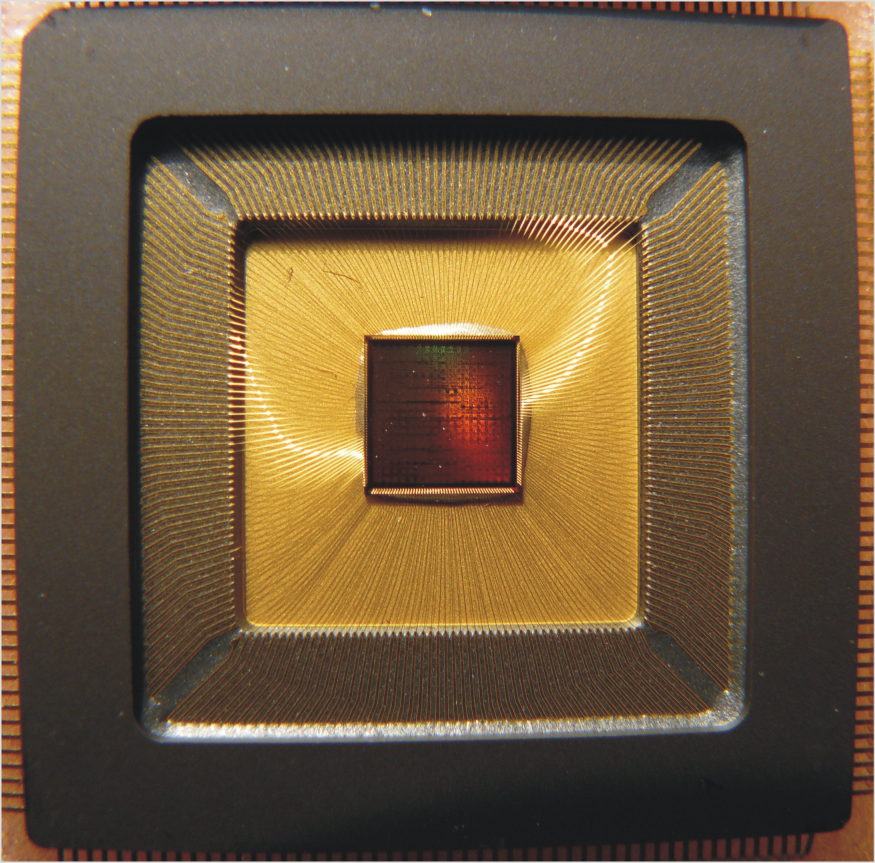

Kurs zawiera materiały do wykładu (slajdy) i laboratorium (instrukcje) z przedmiotu Bloki Funkcjonalne Systemów Elektronicznych.

- Nauczyciel: Andrzej Kwiatkowski

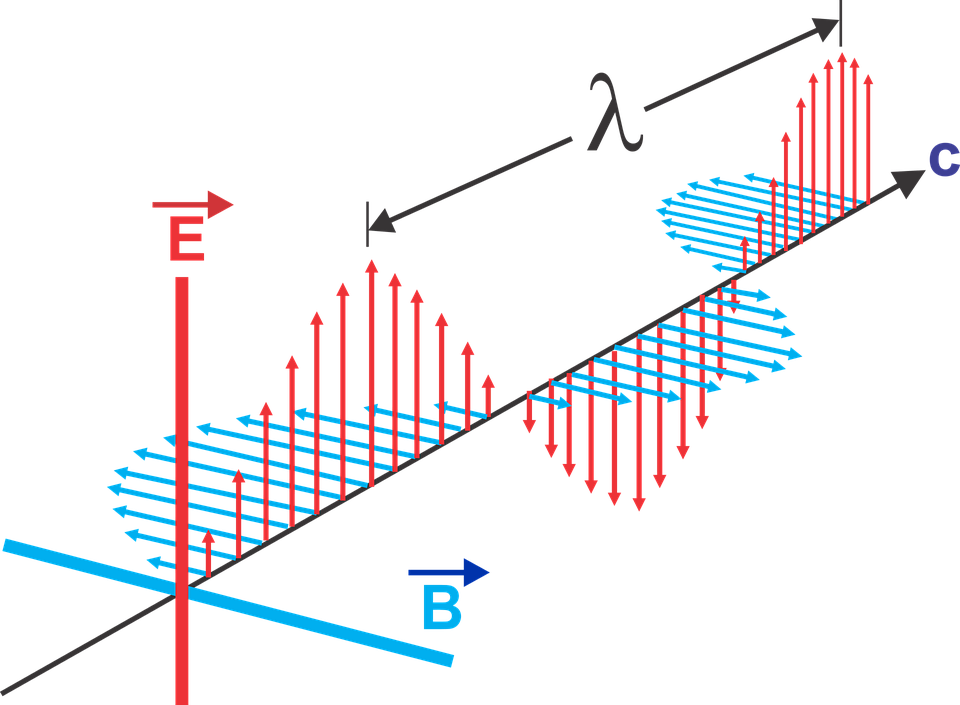

Materiały dydaktyczne z części wykładowej i projektowej z przedmiotu "Anteny i propagacja fal". Studia inżynierskie - semestr 3, kierunek Elektronika i Telekomunikacja

- Nauczyciel: Sławomir Jerzy Ambroziak

- Nauczyciel: Rafał Lech

Kurs dla przedmiotu Systemy radiokomunikacyjne, w którym omawiane będą systemy komórkowe, systemy bezprzewodowej transmisji danych, takie jak WiFi, Bluetooth, Wimax, oraz techniki stosowane w tego typu systemach.

- Nauczyciel: Andrzej Marczak

EiT, studia I stopnia

- Nauczyciel: Arkadiusz Szewczyk

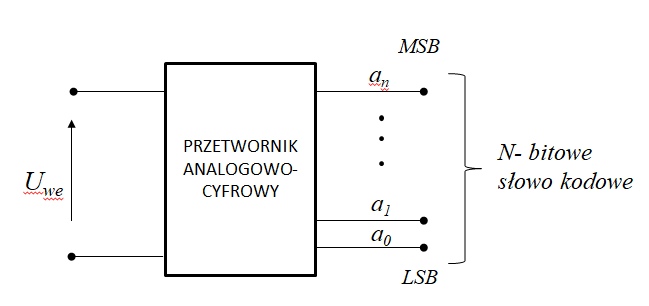

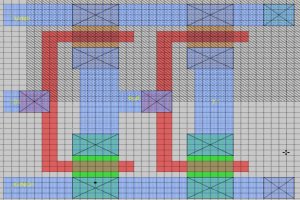

Kurs omawia projektowanie i sposoby realizacji podstawowych konfiguracji układów elektronicznych realizujących funkcje przetwarzania sygnałów w dziedzinie czasu dyskretnego, np. układy całkujące, przetworniki analogowo-cyfrowe i cyfrowo-analogowe, itp.

- Nauczyciel: Grzegorz Blakiewicz

- Nauczyciel: Waldemar Jendernalik

- Nauczyciel: Bogdan Pankiewicz

Przedmiot kursowy dla stopnia I, sem. 7, profil Inżynieria Mikrofalowa i Antenowa

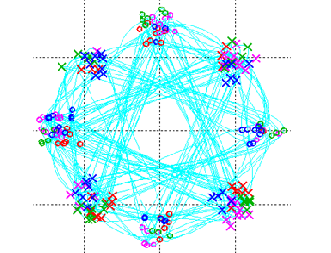

Celem przedmiotu jest wprowadzenie do technik radiowych stosowanych we współczesnych systemach komunikacji bezprzewodowej pod kątem projektowania i doboru układów w torach wysokiej częstotliwości. Studenci poznają najważniejsze metody modulacji i rozpraszania sygnału i ich wrażliwość na niedoskonałości urządzeń zastosowanych w systemie komunikacyjnym. Przedmiot obejmuje wprowadzenie i praktyczna naukę obsługi zaawansowanego narzędzia symulacyjnego, Keysight ADS Communication Designer umożliwiających zintegrowane projektowanie na poziomie układów, podsystemów i całego systemu komunikacyjnego.

- Nauczyciel: Krzysztof Nyka

- Nauczyciel: KAMIL Trzebiatowski

Przedmiot kursowy dla stopnia I, sem. 7, profil Inżynieria Mikrofalowa i Antenowa

Celem jest wprowadzenie do analizy, projektowania i pomiarów podstawowych układów pasywnych (dzielniki, sprzęgacze, filtry), aktywnych (wzmacniacze, oscylatory) i podzespołów półprzewodnikowych (diody, tranzystory) dla zakresu b.w.cz., stosowanych h w urządzeniach i systemach bezprzewodowych. Studenci poznają zasadę działania i obsługę oprogramowania Keysight ADS, które jest zaawansowanym i profesjonalnym narzędziem do analizy i projektowania układów b.w.cz.

- Nauczyciel: Łukasz Kulas

- Nauczyciel: Krzysztof Nyka

- Nauczyciel: Benedykt Sikorski

- Nauczyciel: KAMIL Trzebiatowski

I stopień, Strumień EA, EiT, sem.5

- Nauczyciel: Agnieszka Drewniak

- Nauczyciel: Piotr Jasiński

- Nauczyciel: PAWEŁ Kalinowski

- Nauczyciel: KAMIL Osiński

Kurs e-nauczania przeznaczony na potrzeby przedmiotu "Podstawy systemów informacyjnych" realizowanego na kierunku Elektronika i Telekomunikacja, studia inżynierskie sem. 5

- Nauczyciel: Bartosz Czaplewski

- Nauczyciel: Maciej Sac

1. "Technika obliczeniowa i symulacyjna" - wykład (Metody Numeryczne) dla EiT, sem. 2, na studiach I stopnia

Wykładowca: dr inż. B. Stawarz-Graczyk

2. "Technika obliczeniowa i symulacyjna" - wykład (z zagadnień dotyczących PSpice'a i Matlaba) dla EiT, sem. 2, na studiach I stopnia

Wykładowcy: dr inż. M. S. Makowski (PSpice) i dr inż. Jan Schmidt (Matlab)

Osoba odpowiedzialna za przedmiot: dr inż. Jan Schmidt KSON WETI PG

- Nauczyciel: Marek Makowski

- Nauczyciel: Mariusz Rudnicki

- Nauczyciel: Jan Schmidt

- Nauczyciel: Barbara Stawarz-Graczyk

- Nauczyciel: Arkadiusz Szewczyk

- Nauczyciel: Dorota Toboła

Wykład dla sem. 7, studia I stopnia - inżynierskie, stacjonarne, profil: Sieci teleinformacyjne (EiT),

- Nauczyciel: Magdalena Młynarczuk

Laboratorium dla sem. 7, EiT - telekomunikacja,

profil Sieci Teleinformacyjne

- Nauczyciel: Magdalena Młynarczuk

Materiały wykładowe i ćwiczeniowe z przedmiotu Pola i fale elektromagnetyczne Studia inżynierskie - semestr 3, kierunek Elektronika i Telekomunikacja

Prowadzący:

- dr hab. inż. Piotr Kowalczyk, prof. PG

- dr hab. inż. Rafał Lech, prof. PG

- Nauczyciel: Piotr Kowalczyk

- Nauczyciel: Rafał Lech

- Nauczyciel: MAŁGORZATA Warecka

- Nauczyciel: TOMASZ Chludziński

- Nauczyciel: Barbara Stawarz-Graczyk

- Nauczyciel: Arkadiusz Szewczyk