Kurs wspierający wykład z przedmiotu

Obwody i sygnały

dla kierunku AiR, IBm i EiT sem. 2,

studia I stopnia (WETI PG)

wersja 2023

Prowadzący: Czesław Stefański (cestef@pg.edu.pl) i Iwona Kochańska (iwokocha@pg.edu.pl)

- Nauczyciel: Iwona Kochańska

Wykład na kierunku EiT/ACiR/IBM/INF sem. 2 st. inż.

- Nauczyciel: Sylwia Babicz-Kiewlicz

- Nauczyciel: Stanisław Galla

Kurs składa się z 15 godzinnego wykładu oraz 15 godzinnego laboratorium. Omawiane są najważniejsze zagadnienia dotyczące obwodów zasilających. Na wykładzie omawiane są: podstawowe konfiguracje konwerterów, zasada działania, ważniejsze parametry oraz sposób analizowania i projektowania. W laboratorium wykonywane są dwa rodzaje ćwiczeń. W ćwiczeniach sprzętowych bada się konwertery i dokonuje pomiarów ważniejszych parametrów . W ćwiczeniach symulacyjnych wykorzystuje się symulator obwodów elektrycznych do projektowania i wyznaczania charakterystyk i parametrów konwerterów.

- Nauczyciel: Grzegorz Blakiewicz

Kurs składa się z 15 godzinnego wykładu oraz 15 godzinnego laboratorium. Omawiane są najważniejsze zagadnienia dotyczące zasilaczy systemów elektronicznych. Na wykładzie prezentowane są podstawowe konfiguracje przetwornic impulsowych oraz stabilizatorów napięcia o działaniu ciągłym. Omawiana jest zasada działania, ważniejsze parametry oraz sposób analizowania i projektowania zasilaczy. W laboratorium wykonywane są dwa rodzaje ćwiczeń. W ćwiczeniach sprzętowych bada się różnego rodzaju zasilacze i dokonuje pomiarów ważniejszych parametrów. W ćwiczeniach symulacyjnych wykorzystuje się symulator obwodów elektrycznych do projektowania i wyznaczania charakterystyk i parametrów zasilaczy.

- Nauczyciel: Rafał Lech

- Nauczyciel: Michał Mrozowski

Kurs pomocniczy dla przedmiotu Projektowanie Usług Telekomunikacyjnych realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Kurs pomocniczy dla przedmiotu Systemy Sygnalizacji i Protokoły realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Student zapoznaje się z warstwowymi architekturami logicznymi sieci, klasyfikuje podstawowe problemy komunikacji sieciowej oraz identyfikuje i analizuje wybrane protokoły i mechanizmy sieci LAN i WAN

- Nauczyciel: Krzysztof Gierłowski

- Nauczyciel: JAKUB Grochowski

- Nauczyciel: Michał Hoeft

- Nauczyciel: Krzysztof Nowicki

- Nauczyciel: Zenon Werbowy

Cel przedmiotu: Zapoznanie z metodami projektowania i symulacji cyfrowych układów programowalnych i ASIC z wykorzystaniem języków opisu sprzętu.

Treści przedmiotu:

1. Wprowadzenie, znaczenie i zastosowania języków HDL. Historia powstania języka Verilog.

2. Poziomy opisu sprzętu (Verilog).

3. Metodologie projektowania. Prosty przykład.

4. Składnia języka Verilog.

5. Typy danych.

6. Zadania systemowe i dyrektywy kompilatora.

7. Moduły i porty.

8. Projektowanie na poziomie bramek logicznych.

9. Opóźnienia w bramkach.

10. Modelowanie na poziomie rejestrów.

11. Przypisanie ciągłe.

12. Wyrażenia i operatory.

13. Modelowanie na poziomie behawioralnym.

14. Funkcje i zadania.

15. Techniki modelowania.

16. Verilog 2001 zmiany w standardzie.

17. Geneza powstania języka VHDL.

18. Składnia języka i typy danych

19. Jednostki projektowe i ich architektury.

20. Osadzanie komponentów.

21. Przypisania współbieżne, zwykłe i warunkowe.

22. Opóźnienia, operacje współbieżne oraz czasowe.

23. Procesy.

24. Polecenia warunkowe i pętle.

25. Opóźnienia typu wait.

26. Funkcje i procedury.

27. Biblioteki i pakiety.

28. Biblioteka IEEE.

29. Synteza maszyn stanów.

- Nauczyciel: Marek Wójcikowski

- Nauczyciel: Marcin Gnyba

- Nauczyciel: MONIKA Kosowska

- Nauczyciel: Adam Mazikowski

- Nauczyciel: Małgorzata Szczerska

Cel przedmiotu: Zapoznanie z metodami projektowania i symulacji cyfrowych układów programowalnych i ASIC z wykorzystaniem języków opisu sprzętu.

Treści przedmiotu:

1. Wprowadzenie, znaczenie i zastosowania języków HDL. Historia powstania języka Verilog.

2. Poziomy opisu sprzętu (Verilog).

3. Metodologie projektowania. Prosty przykład.

4. Składnia języka Verilog.

5. Typy danych.

6. Zadania systemowe i dyrektywy kompilatora.

7. Moduły i porty.

8. Projektowanie na poziomie bramek logicznych.

9. Opóźnienia w bramkach.

10. Modelowanie na poziomie rejestrów.

11. Przypisanie ciągłe.

12. Wyrażenia i operatory.

13. Modelowanie na poziomie behawioralnym.

14. Funkcje i zadania.

15. Techniki modelowania.

16. Verilog 2001 zmiany w standardzie.

17. Geneza powstania języka VHDL.

18. Składnia języka i typy danych

19. Jednostki projektowe i ich architektury.

20. Osadzanie komponentów.

21. Przypisania współbieżne, zwykłe i warunkowe.

22. Opóźnienia, operacje współbieżne oraz czasowe.

23. Procesy.

24. Polecenia warunkowe i pętle.

25. Opóźnienia typu wait.

26. Funkcje i procedury.

27. Biblioteki i pakiety.

28. Biblioteka IEEE.

29. Synteza maszyn stanów.

- Nauczyciel: Marek Wójcikowski

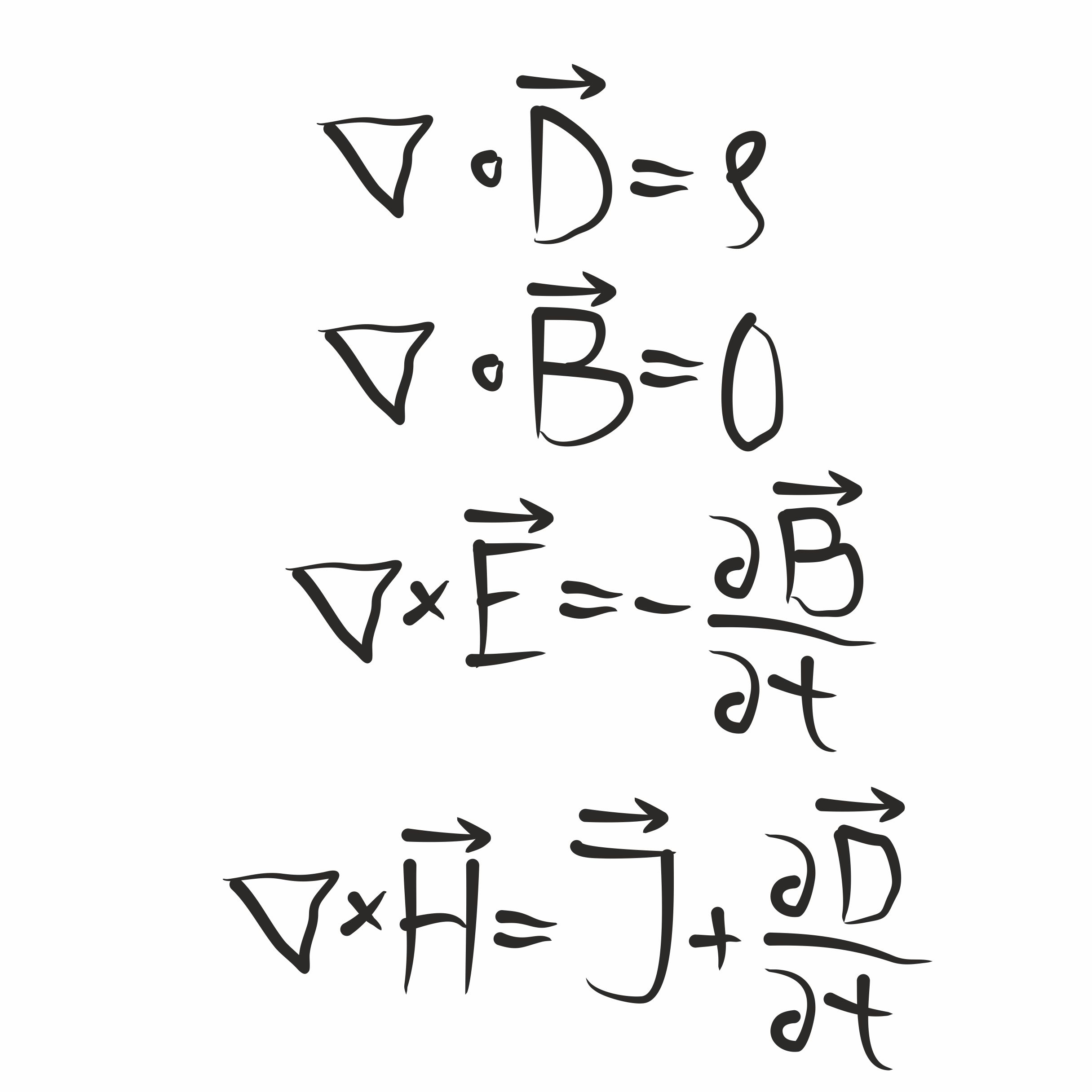

Materiały wykładowe i ćwiczeniowe z przedmiotu Podstawy Elektrodynamiki Studia inżynierskie - semestr 2, kierunek Elektronika i Telekomunikacja

- Nauczyciel: Piotr Kowalczyk

- Nauczyciel: Rafał Lech

- Nauczyciel: MAŁGORZATA Warecka

- Nauczyciel: Włodzimierz Zieniutycz

Materiały wykładowe i ćwiczeniowe z przedmiotu Technika Bardzo Wysokich Częstotliwości Studia inżynierskie - semestr 4, kierunek Elektronika i Telekomunikacja

- Nauczyciel: Piotr Kowalczyk

- Nauczyciel: Adam Lamęcki

- Nauczyciel: Rafał Lech

- Nauczyciel: MAŁGORZATA Warecka

- Nauczyciel: Lech Kilian

- Nauczyciel: Dorota Toboła

- Nauczyciel: Iwona Kochańska

- Nauczyciel: Mariusz Rudnicki

- Nauczyciel: Jan Schmidt

- Nauczyciel: Dorota Toboła

- Nauczyciel: Aleksander Schmidt

- Nauczyciel: Jan Schmidt

- Nauczyciel: Dorota Toboła

I stopień, Strumień EA, EiT, sem.5

- Nauczyciel: Agnieszka Drewniak

- Nauczyciel: PAWEŁ Kalinowski

- Nauczyciel: KAMIL Osiński

EiT, I st., sem. 7, Opto

Kierunek: Elektronika i telekomunikacja

Studia inżynierskie (I stopnia)

Profil: Optoelektronika

Rok 4

Semestr 7

- Nauczyciel: Paweł Wierzba

Kurs omawia projektowanie i sposoby realizacji podstawowych konfiguracji układów elektronicznych realizujących funkcje przetwarzania sygnałów w dziedzinie czasu dyskretnego, np. układy całkujące, przetworniki analogowo-cyfrowe i cyfrowo-analogowe, itp.

- Nauczyciel: Grzegorz Blakiewicz