- Nauczyciel: Małgorzata Gajewska

- Nauczyciel: Jarosław Sadowski

Zapoznanie z budową i możliwościami mikroelektronicznych systemów programowalnych, zbudowanych w oparciu o układy programowalne FPGA. Nauczenie studentów, w jaki sposób wewnątrz jednego układu FPGA utworzyć pełen mikroprocesorowy system wraz z procesorem, magistralami, układami peryferyjnymi i pamięcią. Zapoznanie z metodami uruchamiania takich systemów.

- Nauczyciel: Marek Wójcikowski

- Nauczyciel: Michał Lech

- Nauczyciel: KAROLINA Marciniuk

- Nauczyciel: Piotr Odya

- Nauczyciel: DAWID Weber

- Nauczyciel: Bożena Kostek

- Nauczyciel: Adam Kurowski

- Nauczyciel: Michał Lech

- Nauczyciel: KAROLINA Marciniuk

- Nauczyciel: Piotr Odya

- Nauczyciel: Krzysztof Cisowski

Kurs dla studentów 7 semestru studiów pierwszego stopnia dla kierunku Elektronika i telekomunikacja.

- Nauczyciel: Andrzej Marczak

Seminarium dyplomowe inżynierskie dla sem. VII specjalności Technologie multimedialne organizowane jest w celu ułatwienia studentom przygotowania pracy dyplomowej na studiach I stopnia.

- Nauczyciel: Andrzej Czyżewski

- Nauczyciel: Bożena Kostek

- Nauczyciel: Józef Kotus

- Nauczyciel: Michał Lech

- Nauczyciel: KAROLINA Marciniuk

- Nauczyciel: Mariusz Mróz

- Nauczyciel: Piotr Odya

- Nauczyciel: Paweł Spaleniak

- Nauczyciel: Maciej Szczodrak

- Nauczyciel: Piotr Szczuko

- Nauczyciel: Grzegorz Szwoch

- Nauczyciel: Mariusz Kaczmarek

- Nauczyciel: Magdalena Madej

- Nauczyciel: Tomasz Neumann

- Nauczyciel: Anna Węsierska

Kurs pomocniczy dla przedmiotu Projektowanie Usług Telekomunikacyjnych realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

Kurs pomocniczy dla przedmiotu Systemy Sygnalizacji i Protokoły realizowanego dla studentów I stopnia Wydziału EiT na profilu Sieci Teleinformacyjne.

- Nauczyciel: Marcin Narloch

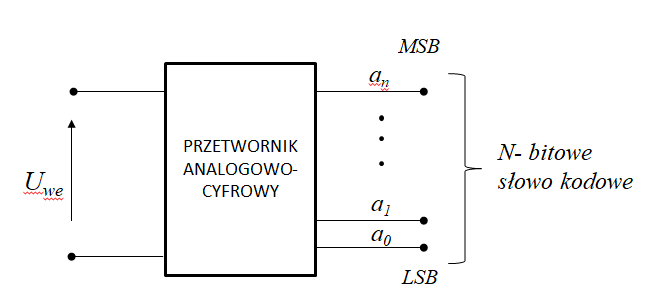

Kurs zawiera materiały do wykładu (slajdy oraz materiały wideo) i laboratorium (instrukcje) z przedmiotu Bloki funkcjonalne Systemów Elektronicznych.

- Nauczyciel: Andrzej Kwiatkowski

Wykład na kierunku EiT sem. 2 st. inż.

- Nauczyciel: Sylwia Babicz-Kiewlicz

- Nauczyciel: Stanisław Galla

W tym miejscu będą zamieszczane zadania wraz z odpowiedziami do samodzielnego rozwiązywania jak również rozwiązane zadania. Kurs przeznaczony jest dla studentów Wydziału ETI - semestr 2. Wykład prowadzi Profesor Możejko.

- Nauczyciel: Daniel Pelczarski

EiT studia I stopinia, sem. zimowy

- Nauczyciel: Magdalena Mazur-Milecka

- Nauczyciel: Jacek Rumiński

- Nauczyciel: ŁUKASZ Woźniak

EiT studia I stopinia, sem. zimowy

- Nauczyciel: Magdalena Mazur-Milecka

- Nauczyciel: Jacek Rumiński

- Nauczyciel: ŁUKASZ Woźniak

Kurs wspomagający realizację przedmiotu Języki programowania wysokiego poziomu. Uczestnikami kursu będą studenci kierunku elektronika i telekomunikacja. Skrót kursu JPWP Dziękuję i pozdrawiam.

- Nauczyciel: Mariusz Kaczmarek

- Nauczyciel: Magdalena Mazur-Milecka

- Nauczyciel: Tomasz Neumann

- Nauczyciel: Jacek Rumiński

Cel przedmiotu: Zapoznanie z metodami projektowania i symulacji cyfrowych układów programowalnych i ASIC z wykorzystaniem języków opisu sprzętu.

Treści przedmiotu:

1. Wprowadzenie, znaczenie i zastosowania języków HDL. Historia powstania języka Verilog.

2. Poziomy opisu sprzętu (Verilog).

3. Metodologie projektowania. Prosty przykład.

4. Składnia języka Verilog.

5. Typy danych.

6. Zadania systemowe i dyrektywy kompilatora.

7. Moduły i porty.

8. Projektowanie na poziomie bramek logicznych.

9. Opóźnienia w bramkach.

10. Modelowanie na poziomie rejestrów.

11. Przypisanie ciągłe.

12. Wyrażenia i operatory.

13. Modelowanie na poziomie behawioralnym.

14. Funkcje i zadania.

15. Techniki modelowania.

16. Verilog 2001 zmiany w standardzie.

17. Geneza powstania języka VHDL.

18. Składnia języka i typy danych

19. Jednostki projektowe i ich architektury.

20. Osadzanie komponentów.

21. Przypisania współbieżne, zwykłe i warunkowe.

22. Opóźnienia, operacje współbieżne oraz czasowe.

23. Procesy.

24. Polecenia warunkowe i pętle.

25. Opóźnienia typu wait.

26. Funkcje i procedury.

27. Biblioteki i pakiety.

28. Biblioteka IEEE.

29. Synteza maszyn stanów.

- Nauczyciel: Adrian Bekasiewicz

- Nauczyciel: Marek Wójcikowski

Kurs składa się z 30 godzinnego wykładu oraz 15 godzinnego laboratorium. Przedstawiane są informacje o układach zasilających realizowanych w formie przetwornic impulsowych. Na wykładzie omawiane są podstawowe konfiguracje przetwornic, zasada działania, ważniejsze parametry oraz sposób analizowania i projektowania. W laboratorium w sposób praktyczny ćwiczy się symulacje działania przetwornic oraz wyznaczanie charakterystyk i podstawowych parametrów.

- Nauczyciel: Grzegorz Blakiewicz

Kurs wspomagający realizację przedmiotu Metody przetwarzania obrazów

I stopień EiT

- Nauczyciel: Tomasz Neumann

- Nauczyciel: Artur Poliński

- Nauczyciel: Anna Węsierska